Триггер

Для реализации хранения данных в оперативной памяти компьютера и внутренних регистрах процессора необходимо устройство способное находится в двух устойчивых состояниях (0 и 1). Такое устройство было изобретено советским ученым-радиотехником Михаилом Александровичем Бонч-Бруевичем в 1918 году на основе лампового триода. В последствие этот элемент получил название триггер (англ.trigger – «спусковой крючок», в общем смысле, приводящий нечто в действие).

Триггер — устройство, способное длительное время находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов.

Один триггер способен хранить один бит данных. Соответственно, для хранения 1 байта информации потребуется 8 триггеров, а для 1 килобайта – 8 • 1024 подобных элемента. Очевидно, что современные объемы оперативной памяти компьютера содержат миллионы триггеров.

Существует несколько видов триггеров. Одним из самых распространённых является RS-триггер

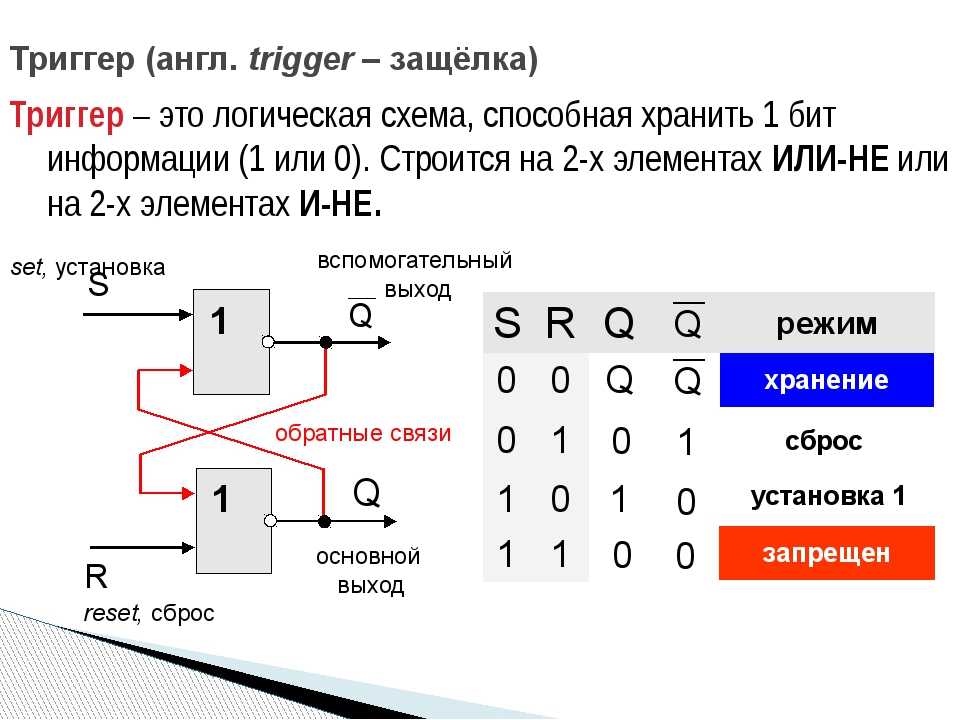

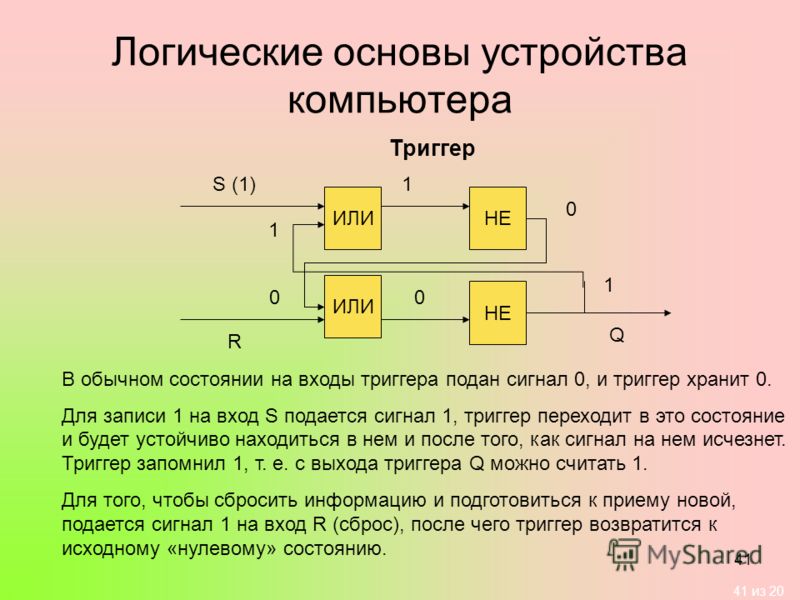

Rs-триггер можно построить на двух дизъюнкторах и двух инверторах. На рисунке 1 показано условное обозначение триггера (слева) и его устройство на указанных логических элементах.

Rs-триггер можно построить на двух дизъюнкторах и двух инверторах. На рисунке 1 показано условное обозначение триггера (слева) и его устройство на указанных логических элементах.Триггер имеет два входа S (от англ. set — установить) и R (от англ. reset — сброс), на которые поступают управляющие сигналы и два выхода — Q и ¬ Q. Основным выходом является Q.

Для реализации возможности хранения информации в устройстве триггера используется обратная связь. Под обратной связью понимают подачу выходного сигнала на вход устройства. Обратная связь имеет перекрестный характер (см. рис.1). Дополнительный выход ¬ Q используется только для обратной связи.

Построим таблицу истинности для триггера.

- S = 0, R = 0. В этом случае на вход элемента «ИЛИ» в нижней ветке поступит сигнал ¬ Q + 0 = ¬ Q. Значит, на выходе Q остается прежнее значение. Аналогично, нетрудно заметить, что сигнал ¬ Q также не меняет своего значения. Таким образом, в данном режиме триггер хранит предыдущее состояние.

- S = 0, R = 1. Т. к. на вход R поступает 1, то на выходе элемента «ИЛИ» в нижней ветке схемы будет 1, а на выходе «НЕ» — ноль. Значит, Q = 0. Тогда на входы элемента «ИЛИ» в верхней ветке поступает два нуля, а на выходе ¬ Q имеем 1. Выход Q является основным, значит, в триггер записан 0.

- S = 1, R = 0. В силу симметрии схемы (см. рис.1), легко заметить, что в этом случае в триггер будет записана 1.

- S = 1, R = 1. Такая комбинация входных сигналов может привести к неоднозначному результату, поэтому такой вариант запрещен.

| S | R | Q | ¬ Q | Режим работы триггера |

|---|---|---|---|---|

| 0 | 0 | Q | ¬ Q | Хранение бита |

| 0 | 1 | 1 | 0 | Сброс в 0 |

| 1 | 0 | 0 | 0 | Установка в 1 |

| 1 | 1 | 1 | 1 | Запрещено |

Справочник «Цифровые Интегральные Микросхемы»

Справочник «Цифровые Интегральные Микросхемы» [ Содержание ] Увлекаетесь электроникой?

Приглашаем Вас принять участие

в бета-тестировании онлайн-редактора

электрических схем.

sapr.asvcorp.ru

Работайте со схемами прямо из браузера.

2.5.1. RS-триггеры

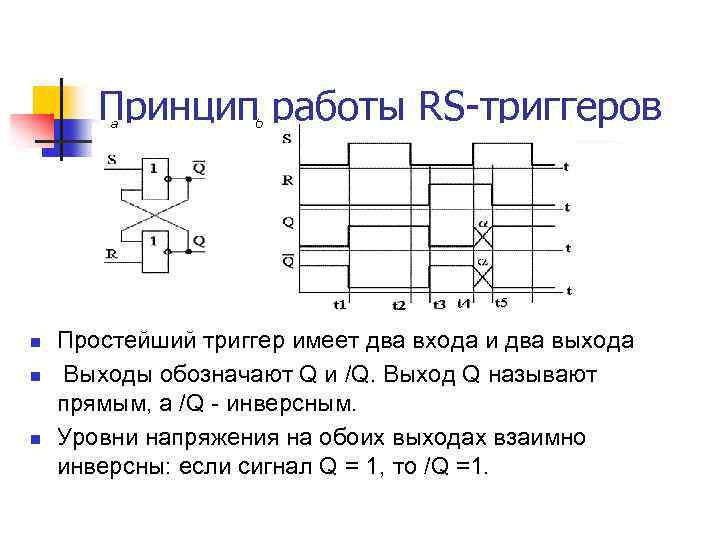

RS-триггер — это триггер с раздельной установкой состояний логического нуля и единицы (с раздельным запуском). Он имеет два информационных входа S и R. По входу S триггер устанавливается в состояние Q=l (/Q=0), а по входу R — в состояние Q = О (/Q = 1).

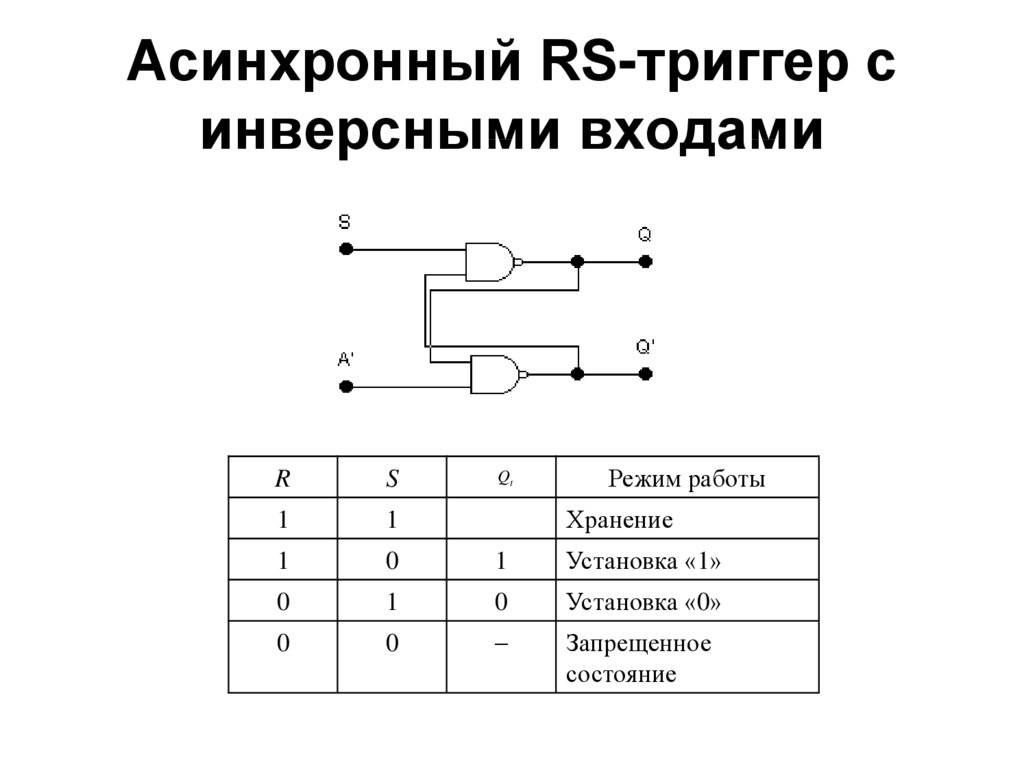

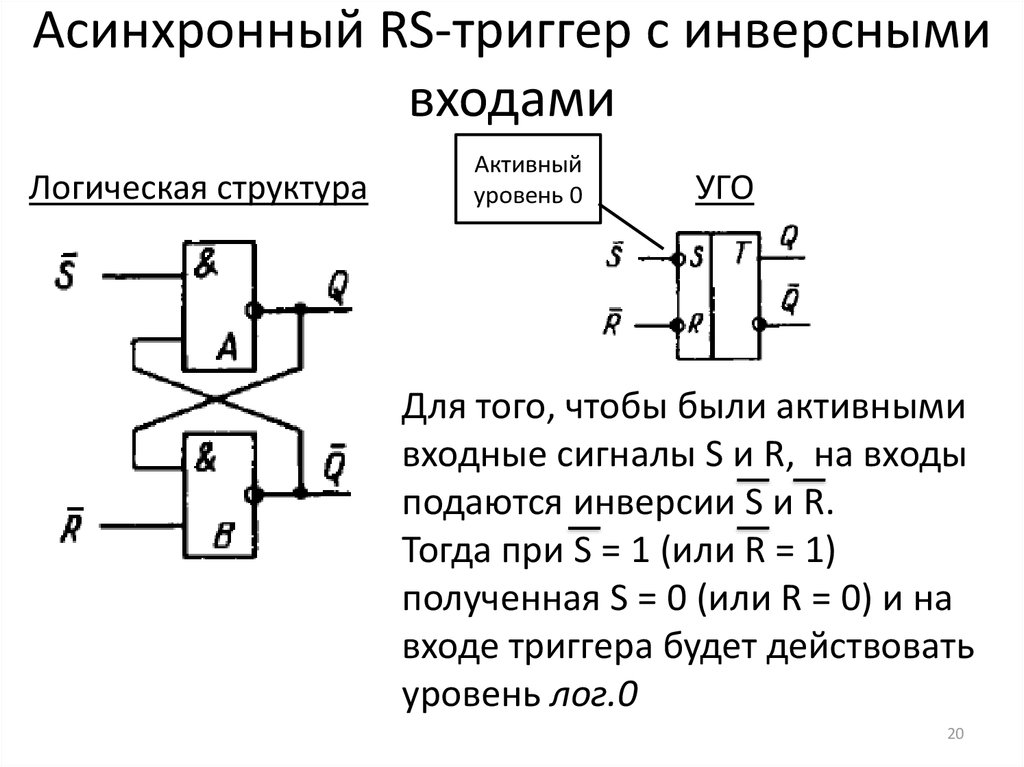

Асинхронные RS-триггеры. Они являются наиболее простыми триггерами.

В качестве самостоятельного устройства применяются редко, но являются

основой для построения более сложных триггеров. В зависимости от

логической структуры различают RS-триггеры с прямыми и инверсными

входами. Их схемы и условные обозначения приведены на рис. 2.37.

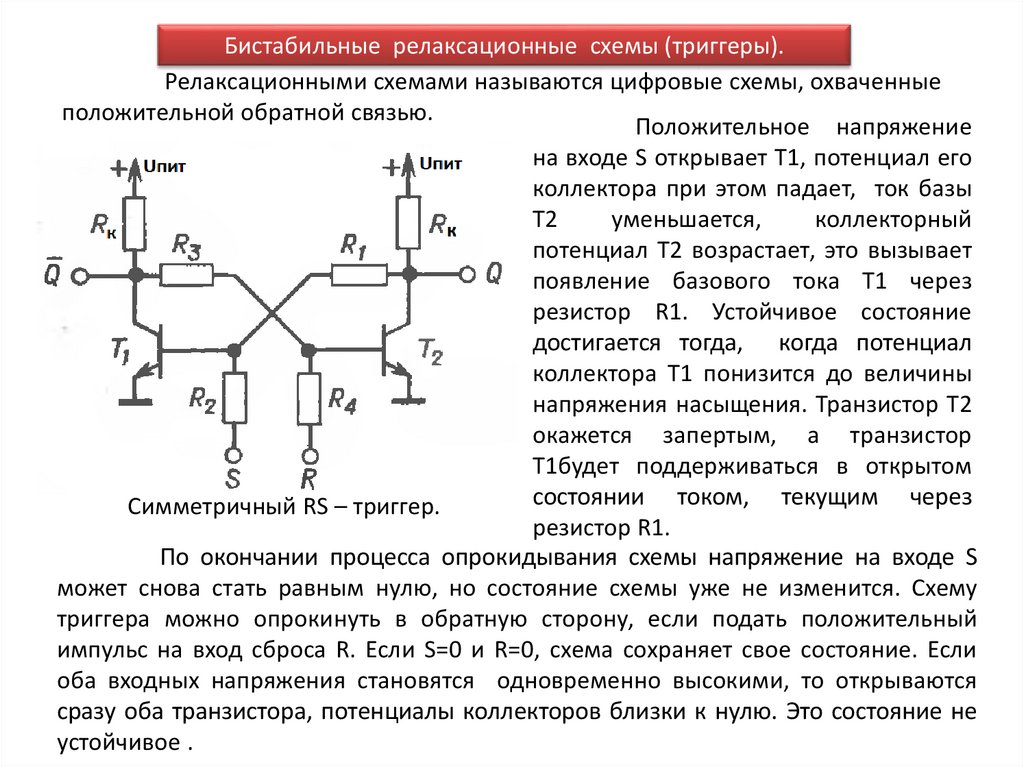

Триггеры такого типа построены на двух логических элементах:

2 ИЛИ-НЕ — триггер с прямыми входами (рис. 2.37, а), 2 И-НЕ — триггер

с инверсными входами (рис. 2.37, б). Выход каждого из логических

элементов подключен к одному из входов другого элемента, что

обеспечивает триггеру два устойчивых состояния.

Рис. 2.37. Асинхронные RS-триггеры: а — RS-триггер на логических элементах ИЛИ-НЕ и условное обозначение; б — RS-триггер на логических элементах И-НЕ и условное обозначение.

Состояния триггеров под воздействием определенной комбинации входных сигналов приведены в таблицах функционирования (состояний) (табл. 2.18).

| Входы | Выходы | ||||

|---|---|---|---|---|---|

| S | R | Логика И-НЕ | Логика ИЛИ-НЕ | ||

| Qn+1 | /Qn+1 | Qn+1 | /Qn+1 | ||

| 0 | 0 | X | Qn | /Qn | |

| 1 | 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | Qn | /Qn | X | |

В таблицах Qn (/Qn) обозначены уровни, которые были на

выходах триггера до подачи на его входы так называемых

активных уровней. Активным называют логический уровень,

действующий на входе логического элемента и однозначно

определяющий логический уровень выходного сигнала

(независимо от логических уровней, действующих на остальных

входах). Для элементов ИЛИ-НЕ за активный уровень принимают

высокий уровень — 1, а для элементов И-НЕ — низкий

уровень — О. Уровни, подача которых на один из входов не

приводит к изменению логического уровня на выходе элемента,

называют пассивными. Уровни Qn+1(/Qn+1) обозначают логические

уровни на выходах триггера после подачи информации на его входы.

Для триггера с прямыми входами при подаче на вход комбинации

сигналов S=1, R=0 на выходе получим Qn+1=1 (/Qn+1=0). Такой

режим называют режимом записи логической единицы.

Активным называют логический уровень,

действующий на входе логического элемента и однозначно

определяющий логический уровень выходного сигнала

(независимо от логических уровней, действующих на остальных

входах). Для элементов ИЛИ-НЕ за активный уровень принимают

высокий уровень — 1, а для элементов И-НЕ — низкий

уровень — О. Уровни, подача которых на один из входов не

приводит к изменению логического уровня на выходе элемента,

называют пассивными. Уровни Qn+1(/Qn+1) обозначают логические

уровни на выходах триггера после подачи информации на его входы.

Для триггера с прямыми входами при подаче на вход комбинации

сигналов S=1, R=0 на выходе получим Qn+1=1 (/Qn+1=0). Такой

режим называют режимом записи логической единицы.

Если со входа S снять единичный сигнал, т. е. установить на входе S нулевой сигнал, то состояние триггера не изменится. Режим S=0, R=0 называют режимом хранения информации, так как информация на выходе остается неизменной.

При подаче входных сигналов S=0, R=1 произойдет переключение триггера,

а на выходе будет Qт+1=0 (/Qn+1=1).

Для триггера с инверсными входами режим записи логической единицы реализуется при /S=0, /R=1, режим записи логического нуля — при /S=1, /R=0. При /S=/R=1 обеспечивается хранение информации. Комбинация входных сигналов /S = /R = 0 является запрещенной.

Микросхема ТР2 включает четыре асинхронных RS-триггера, причем два из

них имеют по два входа установки /S. Управляющим сигналом является уровень

логического нуля (низкий уровень), так как триггеры построены на логических

элементах И-НЕ с обратными связями (т. е. входы инверсные статические).

Установка триггера в состояние высокого или низкого уровня осуществляется

кодом 01 или 10 на входах /S и /R со сменой кода информации.

| Входы | Выход | |||

|---|---|---|---|---|

| /S1 | /S2 | /S | /R | Qn+1 |

| 1 | 1 | 1 | 1 | Qn |

| 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | |||

| 0 | 0 | |||

| 1 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1* |

| 1 | 0 | |||

| 0 | 0 | |||

Временные диаграммы его работы, а также цоколевка представлены на рис. 2.38

Рис. 2.38. Условное обозначение, цоколевка и временные диаграммы работы микросхем типа ТР.

Основные параметры приведены в табл. 2.20б.

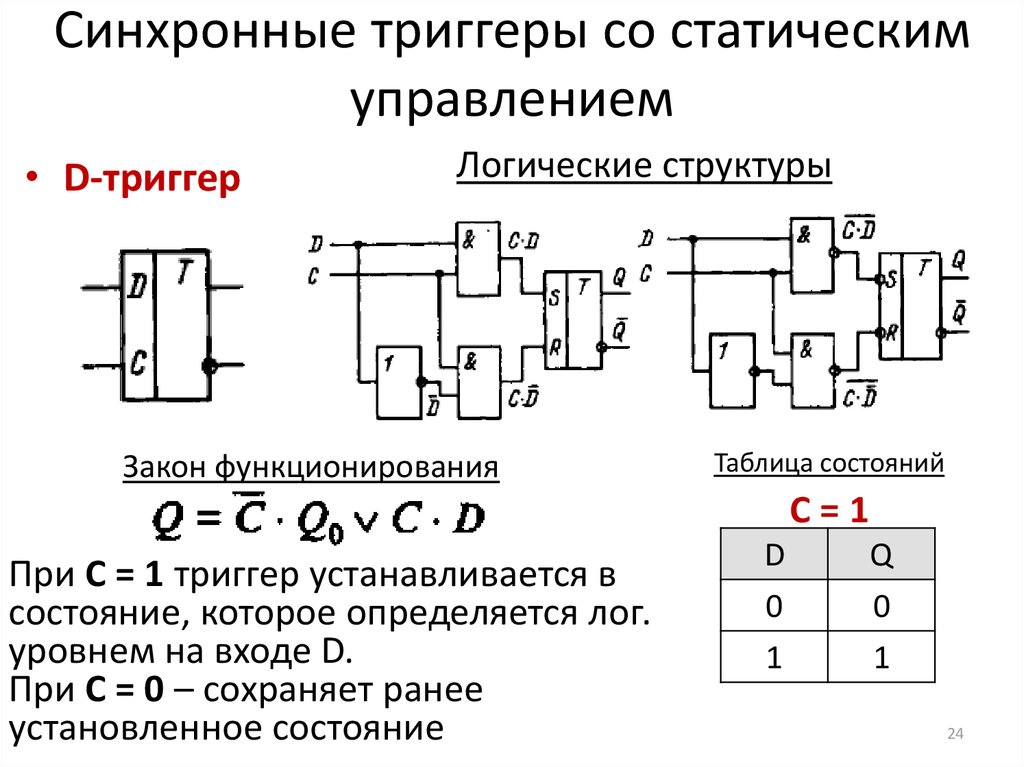

Синхронные RS-триггеры. Триггерные ячейки — это основа делителей частоты, счетчиков и регистров. В этих устройствах записанную ранее информацию по специальному сигналу, называемому тактовым, следует передать на выход и переписать в следующую ячейку. Для осуществления такого режима в RS-триггер необходимо ввести дополнительный вход С, который может быть статическим или динамическим, т. е. получим синхронный RS-триггер.

Схема синхронного RS-триггера на логических элементах И-НЕ со статическим управлением записью (вход С — статический) и его условное обозначение приведены на рис. 2.39, а.

Рис. 2.39. Синхронные RS-триггеры: а — синхронный RS-триггер на элементах И-НЕ и условное обозначение;

б — синхронный RS-триггер на элементах ИЛИ-НЕ и условное обозначение.

Элементы DD1.1 и DD1.2 образуют схему управления, а элементы DD1.3 и DD1.4 — асинхронный RS-триггер. Иногда такой триггер называют RST-триггером (если вход С считать тактовым входом Т).

Триггер имеет прямые статические входы, поэтому управляющим сигналом является уровень логической единицы.

Если на вход С подать сигнал логической единицы C=1, то работа триггера аналогична работе простейшего асинхронного RS-триггера. При C=0 входы S и R не оказывают влияние на состояние триггера. Комбинация сигналов S=R=C=1 является запрещенной. Табл. 2.21 отражает состояния такого триггера.

Синхронный RS-триггер, выполненный на элементах ИЛИ-НЕ, будет иметь инверсные статические входы (рис. 2.39,б). Его функционирование будет определяться таблицей состояний при /C=0 (табл. 2.22). Запрещенной комбинацией входных сигналов будет комбинация /S=/R=/C=0.

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Синхронный RS-триггер с динамическим управлением записью функционирует согласно сигналам, которые были на информационных входах S и R к моменту появления перепада на входе С. Схема такого триггера, его условное обозначение даны на рис. 2.40.

Рис. 2.40. Синхронный RS-триггер с динамическим управлением на логических элементах И-НЕ и условное обозначение.

Элементы DD1.1 … DD1.4 образуют схему управления,

а DD1.5 и DD1.6 — асинхронный RS-триггер, выполняющий роль

элемента памяти. У данного триггера входы /S и /R инверсные

статические (управляющий сигнал — уровень логического нуля),

вход С — прямой динамический. Новое состояние триггера устанавливается

положительным перепадом напряжения (от уровня логического нуля до

уровня логической единицы) на входе С в соответствии с сигналами на

информационных входах /S и /R. Функционирование триггера при некоторых

комбинациях входных сигналов можнопроследить с помощью таблицы

состояний (табл. 2.23).

У данного триггера входы /S и /R инверсные

статические (управляющий сигнал — уровень логического нуля),

вход С — прямой динамический. Новое состояние триггера устанавливается

положительным перепадом напряжения (от уровня логического нуля до

уровня логической единицы) на входе С в соответствии с сигналами на

информационных входах /S и /R. Функционирование триггера при некоторых

комбинациях входных сигналов можнопроследить с помощью таблицы

состояний (табл. 2.23).

| Входы | Внутренние выходы | Выходы | ||||||

| /S | /R | C | A1 | A2 | A3 | A4 | Q | /Q |

|---|---|---|---|---|---|---|---|---|

| 1 | 1 | X | 0 | 1 | 1 | 0 | 0 | 1 |

| 0 | 1 | X | 1 | 1 | 1 | 0 | 0 | 1 |

| 0 | 1 | _/ | 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | _/ | 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | X | 0 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | _/ | 0 | 1 | 0 | 1 | 0 | 1 |

Синхронный двухступенчатый RS-триггер (master-slave,

что переводится «мастер-помощник») состоит из двух синхронных

RS-триггеров и инвертора, рис. 2.41, а. Входы С обоих триггеров

соединены между собой через инвертор DD1.1. Если C=1,

то первый триггер функционирует согласно сигналам на его входах S и R.

Второй триггер функционировать не-может, т. к, у него C=0.

Если C=0, то первый триггер не функционирует, а для второго

триггера C=1, и он изменяет свое состояние согласно сигналам

на выходах первого триггера.

2.41, а. Входы С обоих триггеров

соединены между собой через инвертор DD1.1. Если C=1,

то первый триггер функционирует согласно сигналам на его входах S и R.

Второй триггер функционировать не-может, т. к, у него C=0.

Если C=0, то первый триггер не функционирует, а для второго

триггера C=1, и он изменяет свое состояние согласно сигналам

на выходах первого триггера.

Рис. 2.41. Синхронный двухступенчатый RS-триггер: a — схема триггера на логических элементах И-НЕ;

б — условное обозначение и временные диаграммы тактового импульса.

На рис. 2.41, б показано, что двухступенчатым триггером

управляет полный (фронтом и срезом) тактовый импульс С.

Если каждый из триггеров имеет установку положительным перепадом,

то входная RS-комбинация будет записана в первую ступень в момент

прихода положительного перепада тактового импульса С. В этот момент

во вторую ступень информация попасть не может. Когда придет

отрицательный перепад тактового импульса С, на выходе инвертора

DD1. 1 он появится как положительный. Следовательно, положительный

перепад импульса /С перепишет данные от выходов первого триггера

в триггер второй ступени. Сигнал на выходе появится с задержкой,

равной длительности тактового импульса.

1 он появится как положительный. Следовательно, положительный

перепад импульса /С перепишет данные от выходов первого триггера

в триггер второй ступени. Сигнал на выходе появится с задержкой,

равной длительности тактового импульса.

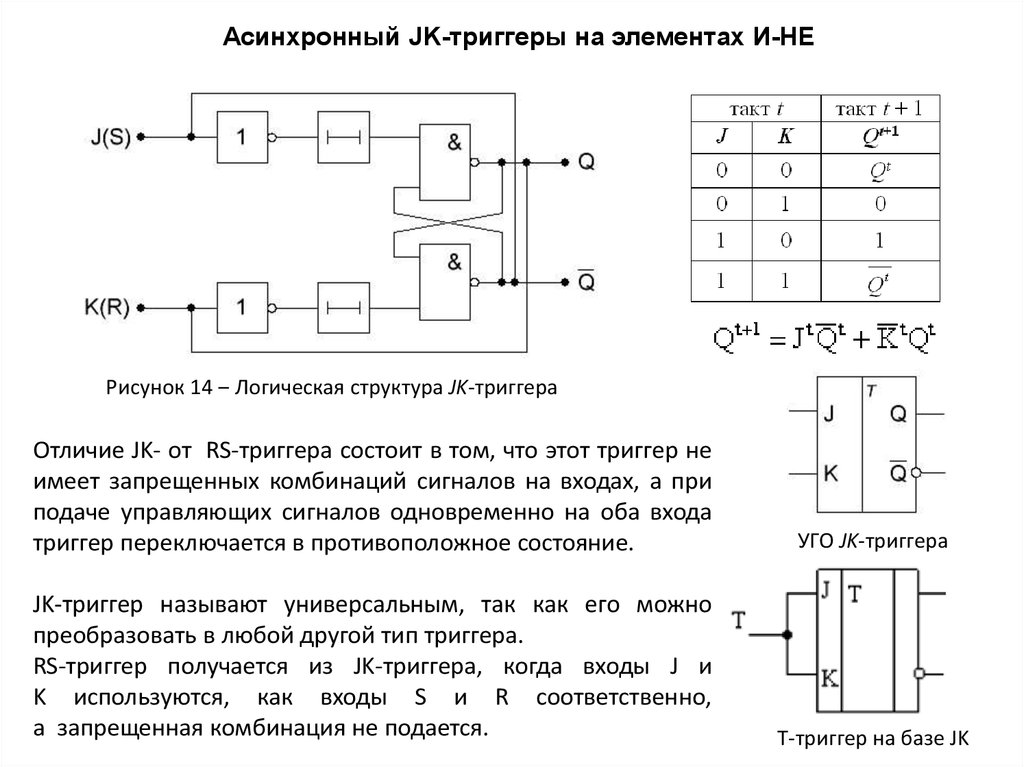

Очень часто необходимо использовать триггер для деления частоты входной последовательности импульсов на два, т. е. производить переключение триггера в новое состояние каждым входным импульсом (фронтом или спадом). Такой триггер называют счетным, или T-триггером (от англ. Toggle). Он имеет один управляющий вход Т. В сериях выпускаемых микросхем T-триггеров нет. Но триггер такого типа может быть создан на базе синхронного RS-триггера с динамическим управлением, если прямой выход Q соединить с инверсным входом /S, а инверсный выход /Q соединить с инверсным входом /R. На вход синхронизации С подать входную последовательность импульсов (т. е. это будет T-вход). На рис. 2.42 показана схема такого триггера и временные диаграммы его работы.

Рис.

22.

22.