Справочник «Цифровые Интегральные Микросхемы»

Справочник «Цифровые Интегральные Микросхемы» [ Содержание ] Увлекаетесь электроникой?

Приглашаем Вас принять участие

в бета-тестировании онлайн-редактора

электрических схем.

sapr.asvcorp.ru

Работайте со схемами прямо из браузера.

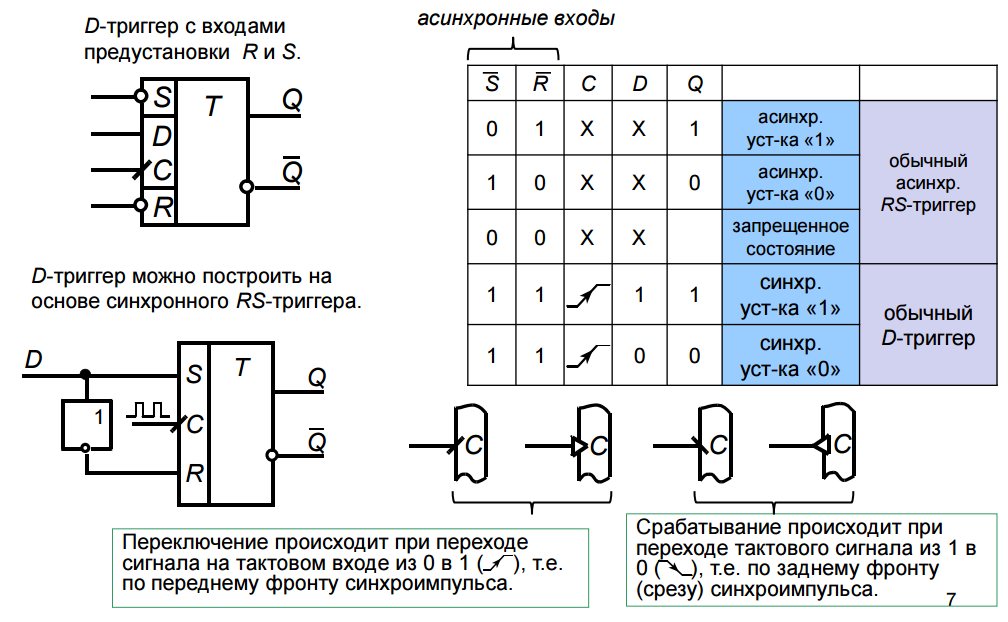

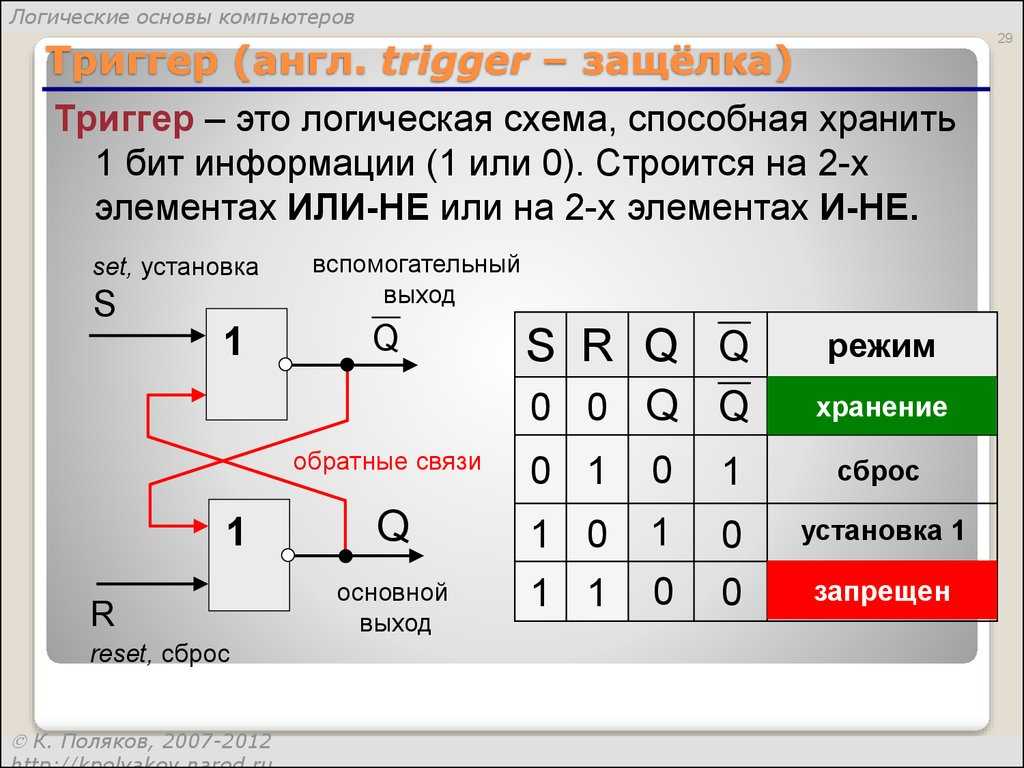

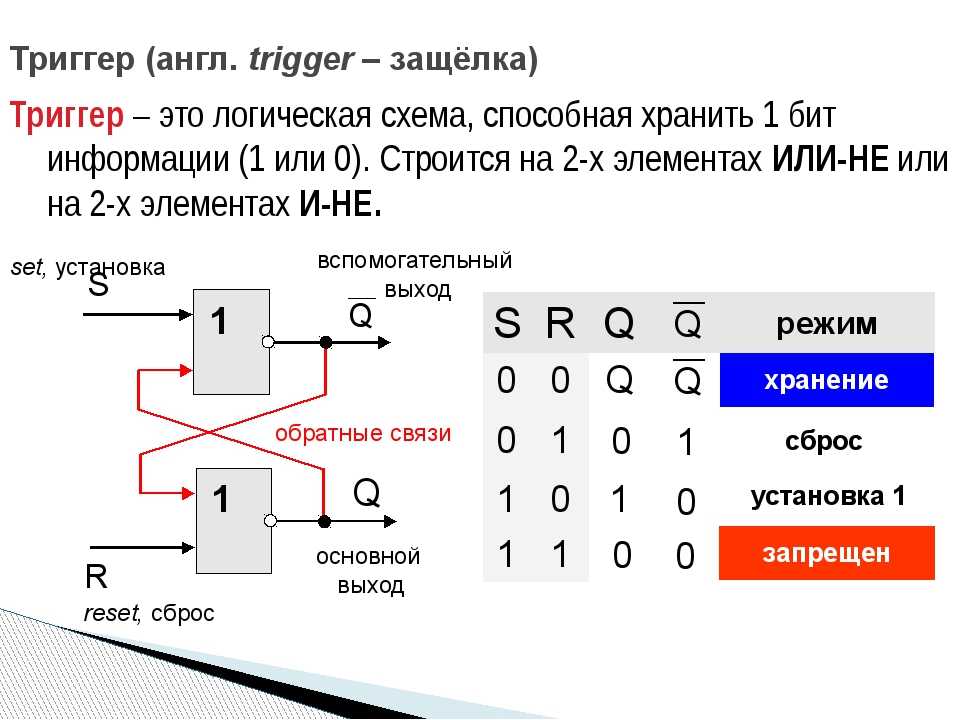

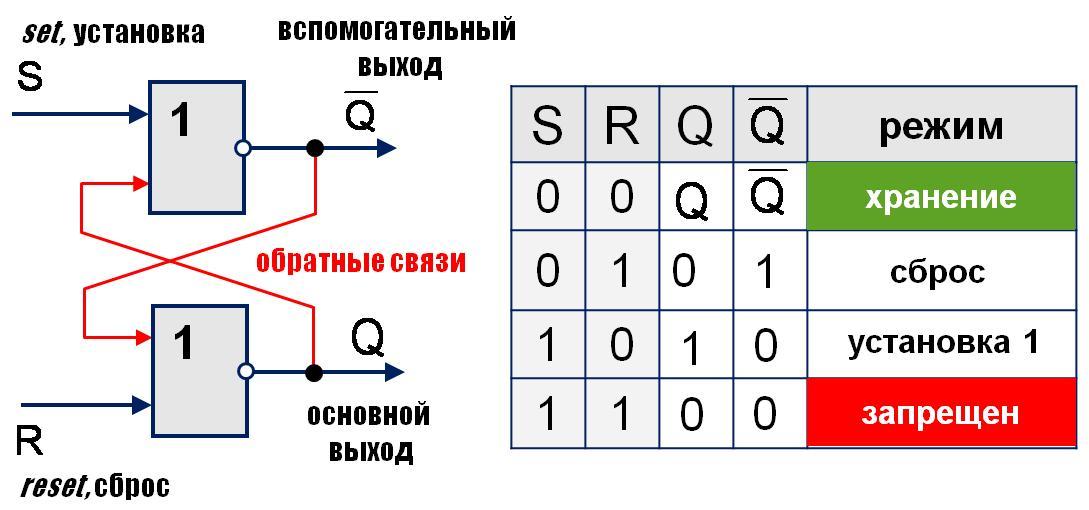

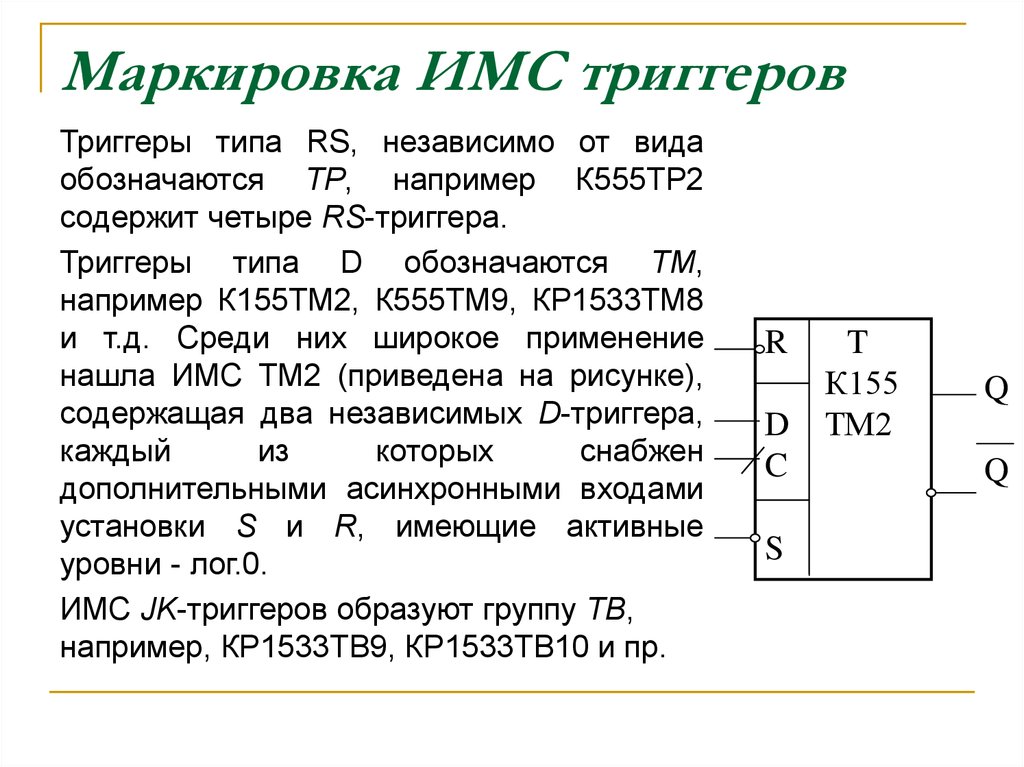

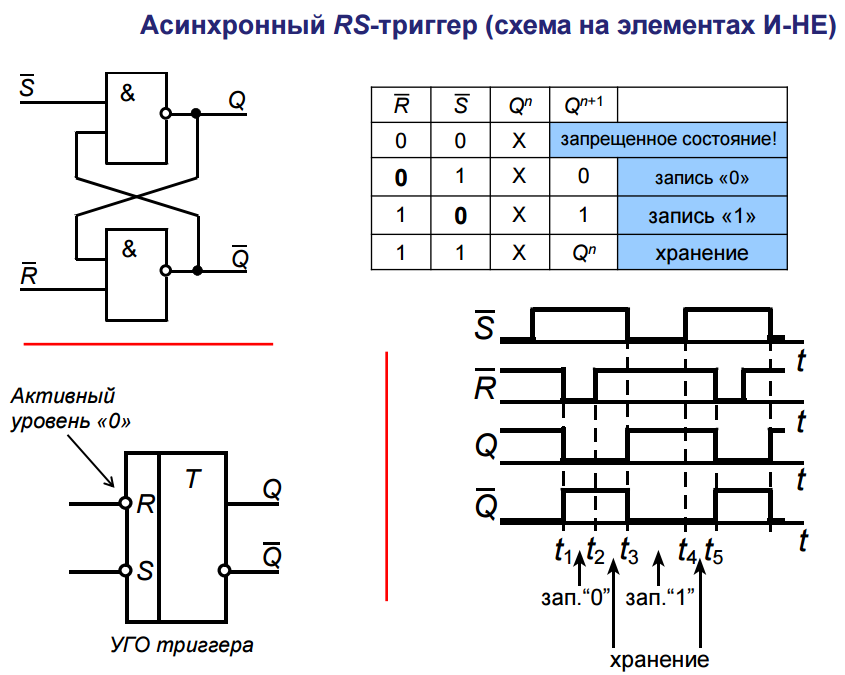

2.5.1. RS-триггеры

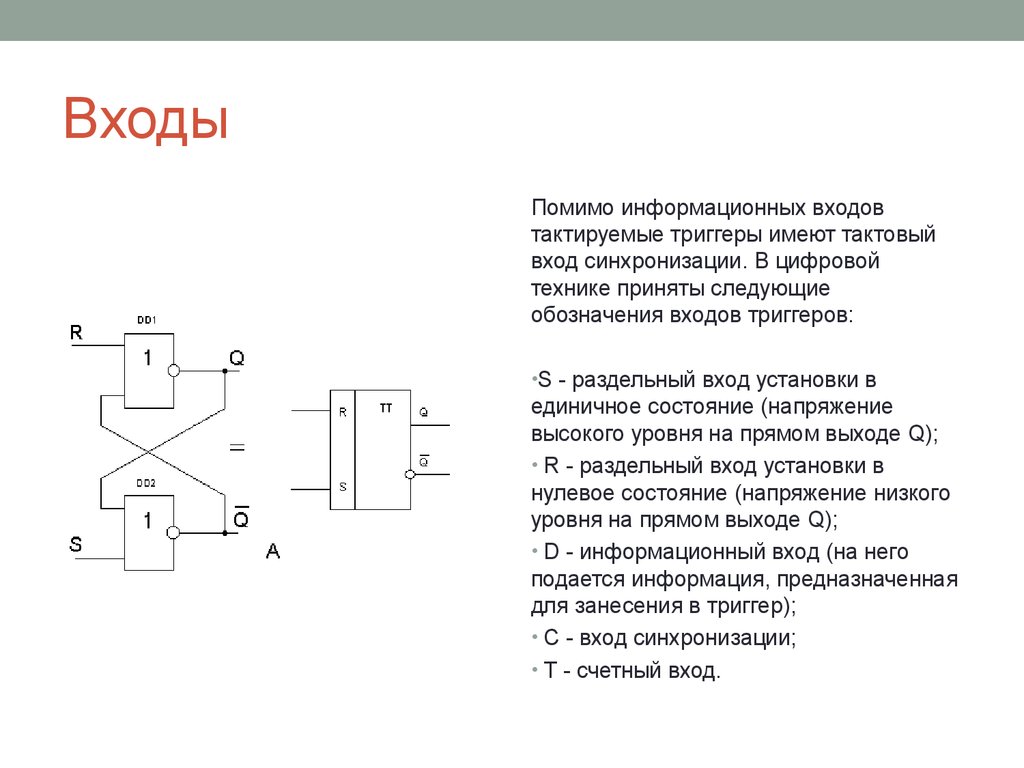

RS-триггер — это триггер с раздельной установкой состояний логического нуля и единицы (с раздельным запуском). Он имеет два информационных входа S и R. По входу S триггер устанавливается в состояние Q=l (/Q=0), а по входу R — в состояние Q = О (/Q = 1).

Асинхронные RS-триггеры. Они являются наиболее простыми триггерами.

В качестве самостоятельного устройства применяются редко, но являются

основой для построения более сложных триггеров. В зависимости от

логической структуры различают RS-триггеры с прямыми и инверсными

входами. Их схемы и условные обозначения приведены на рис. 2.37.

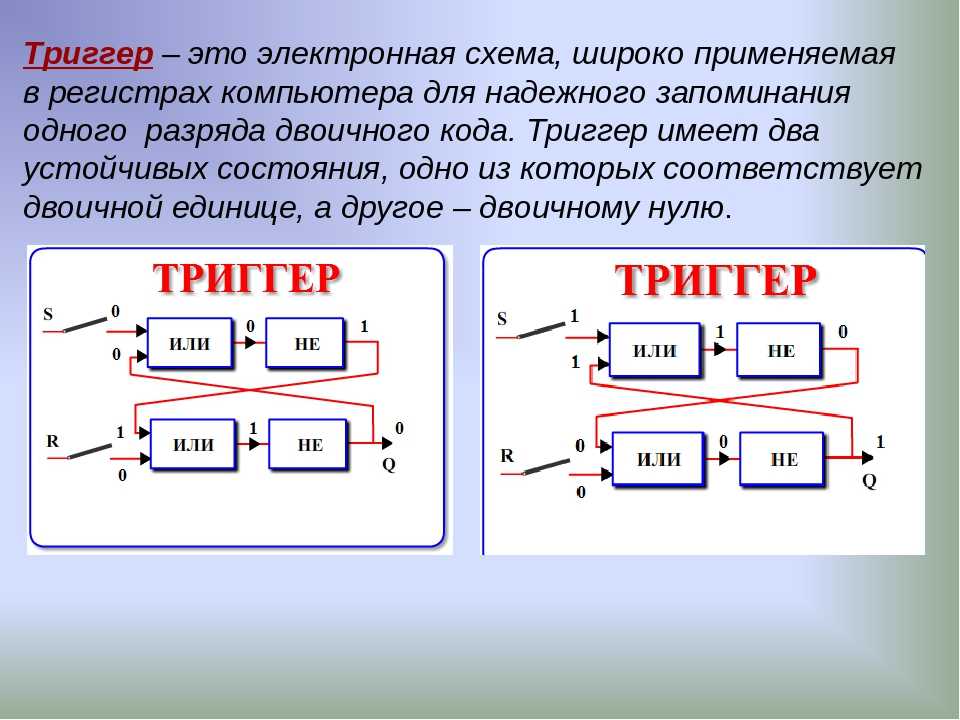

Триггеры такого типа построены на двух логических элементах:

2 ИЛИ-НЕ — триггер с прямыми входами (рис.

Рис. 2.37. Асинхронные RS-триггеры: а — RS-триггер на логических элементах ИЛИ-НЕ и условное обозначение; б — RS-триггер на логических элементах И-НЕ и условное обозначение.

Состояния триггеров под воздействием определенной комбинации входных сигналов приведены в таблицах функционирования (состояний) (табл. 2.18).

| Входы | Выходы | ||||

|---|---|---|---|---|---|

| S | R | Логика И-НЕ | Логика ИЛИ-НЕ | ||

| Qn+1 | /Qn+1 | Qn+1 | /Qn+1 | ||

| 0 | 0 | X | Qn | /Qn | |

| 1 | 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | Qn | /Qn | X | |

В таблицах Qn (/Qn) обозначены уровни, которые были на

выходах триггера до подачи на его входы так называемых

активных уровней. Активным называют логический уровень,

действующий на входе логического элемента и однозначно

определяющий логический уровень выходного сигнала

(независимо от логических уровней, действующих на остальных

входах). Для элементов ИЛИ-НЕ за активный уровень принимают

высокий уровень — 1, а для элементов И-НЕ — низкий

уровень — О. Уровни, подача которых на один из входов не

приводит к изменению логического уровня на выходе элемента,

называют пассивными. Уровни Qn+1(/Qn+1) обозначают логические

уровни на выходах триггера после подачи информации на его входы.

Для триггера с прямыми входами при подаче на вход комбинации

сигналов S=1, R=0 на выходе получим Qn+1=1 (/Qn+1=0). Такой

режим называют режимом записи логической единицы.

Активным называют логический уровень,

действующий на входе логического элемента и однозначно

определяющий логический уровень выходного сигнала

(независимо от логических уровней, действующих на остальных

входах). Для элементов ИЛИ-НЕ за активный уровень принимают

высокий уровень — 1, а для элементов И-НЕ — низкий

уровень — О. Уровни, подача которых на один из входов не

приводит к изменению логического уровня на выходе элемента,

называют пассивными. Уровни Qn+1(/Qn+1) обозначают логические

уровни на выходах триггера после подачи информации на его входы.

Для триггера с прямыми входами при подаче на вход комбинации

сигналов S=1, R=0 на выходе получим Qn+1=1 (/Qn+1=0). Такой

режим называют режимом записи логической единицы.

Если со входа S снять единичный сигнал, т. е. установить на входе S нулевой сигнал, то состояние триггера не изменится. Режим S=0, R=0 называют режимом хранения информации, так как информация на выходе остается неизменной.

При подаче входных сигналов S=0, R=1 произойдет переключение триггера,

а на выходе будет Qт+1=0 (/Qn+1=1). Такой режим называют режимом записи

логического нуля (режим сброса). При S=R=1 состояние триггера будет

неопределенным, так как во время действия информационных сигналов

логические уровни на выходах триггера одинаковы (Qn+1=/Qn+1=0),

а после окончания их действия триггер может равновероятно принять

любое из двух устойчивых состояний. Поэтому такая комбинация S=R=1

является запрещенной.

Такой режим называют режимом записи

логического нуля (режим сброса). При S=R=1 состояние триггера будет

неопределенным, так как во время действия информационных сигналов

логические уровни на выходах триггера одинаковы (Qn+1=/Qn+1=0),

а после окончания их действия триггер может равновероятно принять

любое из двух устойчивых состояний. Поэтому такая комбинация S=R=1

является запрещенной.

Для триггера с инверсными входами режим записи логической единицы реализуется при /S=0, /R=1, режим записи логического нуля — при /S=1, /R=0. При /S=/R=1 обеспечивается хранение информации. Комбинация входных сигналов /S = /R = 0 является запрещенной.

Микросхема ТР2 включает четыре асинхронных RS-триггера, причем два из

них имеют по два входа установки /S. Управляющим сигналом является уровень

логического нуля (низкий уровень), так как триггеры построены на логических

элементах И-НЕ с обратными связями (т. е. входы инверсные статические).

Установка триггера в состояние высокого или низкого уровня осуществляется

кодом 01 или 10 на входах /S и /R со сменой кода информации. Если на входах /S1 = /S2 = /R = 0, то на выходе Q появится напряжение

высокого уровня — 1. Однако это состояние не будет зафиксировано,

«защелкнуто»; если входные уровни 0 убрать, на выходе Q появится

неопределенное состояние. При подаче на входы /S1 = /S2 = R = 1 напряжение

на выходе останется без изменения. Достаточно на одном из входов /S триггера

установить низкий уровень напряжения — 0, а на входе /R высокий уровень

напряжения — 1, и триггер установится в состояние высокого уровня

Qn+1 = 1. Табл. 2.19 дает состояния одного из триггеров микросхемы TP2.

Если на входах /S1 = /S2 = /R = 0, то на выходе Q появится напряжение

высокого уровня — 1. Однако это состояние не будет зафиксировано,

«защелкнуто»; если входные уровни 0 убрать, на выходе Q появится

неопределенное состояние. При подаче на входы /S1 = /S2 = R = 1 напряжение

на выходе останется без изменения. Достаточно на одном из входов /S триггера

установить низкий уровень напряжения — 0, а на входе /R высокий уровень

напряжения — 1, и триггер установится в состояние высокого уровня

Qn+1 = 1. Табл. 2.19 дает состояния одного из триггеров микросхемы TP2.

| Входы | Выход | |||

|---|---|---|---|---|

| /S1 | /S2 | /S | /R | Qn+1 |

| 1 | 1 | 1 | 1 | Qn |

| 0 | 1 | 0 | 1 | 1 |

| 1 | 0 | |||

| 0 | 0 | |||

| 1 | 1 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1* |

| 1 | 0 | |||

| 0 | 0 | |||

Временные диаграммы его работы, а также цоколевка представлены на рис. 2.38

Рис. 2.38. Условное обозначение, цоколевка и временные диаграммы работы микросхем типа ТР.

Основные параметры приведены в табл. 2.20б.

Синхронные RS-триггеры. Триггерные ячейки — это основа делителей частоты, счетчиков и регистров. В этих устройствах записанную ранее информацию по специальному сигналу, называемому тактовым, следует передать на выход и переписать в следующую ячейку. Для осуществления такого режима в RS-триггер необходимо ввести дополнительный вход С, который может быть статическим или динамическим, т. е. получим синхронный RS-триггер.

Схема синхронного RS-триггера на логических элементах И-НЕ со статическим управлением записью (вход С — статический) и его условное обозначение приведены на рис. 2.39, а.

Рис. 2.39. Синхронные RS-триггеры: а — синхронный RS-триггер на элементах И-НЕ и условное обозначение;

б — синхронный RS-триггер на элементах ИЛИ-НЕ и условное обозначение.

Элементы DD1.1 и DD1.2 образуют схему управления, а элементы DD1.3 и DD1.4 — асинхронный RS-триггер. Иногда такой триггер называют RST-триггером (если вход С считать тактовым входом Т).

Триггер имеет прямые статические входы, поэтому управляющим сигналом является уровень логической единицы.

Если на вход С подать сигнал логической единицы C=1, то работа триггера аналогична работе простейшего асинхронного RS-триггера. При C=0 входы S и R не оказывают влияние на состояние триггера. Комбинация сигналов S=R=C=1 является запрещенной. Табл. 2.21 отражает состояния такого триггера.

Синхронный RS-триггер, выполненный на элементах ИЛИ-НЕ, будет иметь инверсные статические входы (рис. 2.39,б). Его функционирование будет определяться таблицей состояний при /C=0 (табл. 2.22). Запрещенной комбинацией входных сигналов будет комбинация /S=/R=/C=0.

|

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Синхронный RS-триггер с динамическим управлением записью функционирует согласно сигналам, которые были на информационных входах S и R к моменту появления перепада на входе С. Схема такого триггера, его условное обозначение даны на рис. 2.40.

Рис. 2.40. Синхронный RS-триггер с динамическим управлением на логических элементах И-НЕ и условное обозначение.

Элементы DD1.1 … DD1.4 образуют схему управления,

а DD1.5 и DD1.6 — асинхронный RS-триггер, выполняющий роль

элемента памяти. У данного триггера входы /S и /R инверсные

статические (управляющий сигнал — уровень логического нуля),

вход С — прямой динамический. Новое состояние триггера устанавливается

положительным перепадом напряжения (от уровня логического нуля до

уровня логической единицы) на входе С в соответствии с сигналами на

информационных входах /S и /R. Функционирование триггера при некоторых

комбинациях входных сигналов можнопроследить с помощью таблицы

состояний (табл. 2.23).

У данного триггера входы /S и /R инверсные

статические (управляющий сигнал — уровень логического нуля),

вход С — прямой динамический. Новое состояние триггера устанавливается

положительным перепадом напряжения (от уровня логического нуля до

уровня логической единицы) на входе С в соответствии с сигналами на

информационных входах /S и /R. Функционирование триггера при некоторых

комбинациях входных сигналов можнопроследить с помощью таблицы

состояний (табл. 2.23).

| Входы | Внутренние выходы | Выходы | ||||||

| /S | /R | C | A1 | A2 | A3 | A4 | Q | /Q |

|---|---|---|---|---|---|---|---|---|

| 1 | 1 | X | 0 | 1 | 1 | 0 | 0 | 1 |

| 0 | 1 | X | 1 | 1 | 1 | 0 | 0 | 1 |

| 0 | 1 | _/ | 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | _/ | 1 | 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | X | 0 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | _/ | 0 | 1 | 0 | 1 | 0 | 1 |

Синхронный двухступенчатый RS-триггер (master-slave,

что переводится «мастер-помощник») состоит из двух синхронных

RS-триггеров и инвертора, рис. 2.41, а. Входы С обоих триггеров

соединены между собой через инвертор DD1.1. Если C=1,

то первый триггер функционирует согласно сигналам на его входах S и R.

Второй триггер функционировать не-может, т. к, у него C=0.

Если C=0, то первый триггер не функционирует, а для второго

триггера C=1, и он изменяет свое состояние согласно сигналам

на выходах первого триггера.

2.41, а. Входы С обоих триггеров

соединены между собой через инвертор DD1.1. Если C=1,

то первый триггер функционирует согласно сигналам на его входах S и R.

Второй триггер функционировать не-может, т. к, у него C=0.

Если C=0, то первый триггер не функционирует, а для второго

триггера C=1, и он изменяет свое состояние согласно сигналам

на выходах первого триггера.

Рис. 2.41. Синхронный двухступенчатый RS-триггер: a — схема триггера на логических элементах И-НЕ;

б — условное обозначение и временные диаграммы тактового импульса.

На рис. 2.41, б показано, что двухступенчатым триггером

управляет полный (фронтом и срезом) тактовый импульс С.

Если каждый из триггеров имеет установку положительным перепадом,

то входная RS-комбинация будет записана в первую ступень в момент

прихода положительного перепада тактового импульса С. В этот момент

во вторую ступень информация попасть не может. Когда придет

отрицательный перепад тактового импульса С, на выходе инвертора

DD1. 1 он появится как положительный. Следовательно, положительный

перепад импульса /С перепишет данные от выходов первого триггера

в триггер второй ступени. Сигнал на выходе появится с задержкой,

равной длительности тактового импульса.

1 он появится как положительный. Следовательно, положительный

перепад импульса /С перепишет данные от выходов первого триггера

в триггер второй ступени. Сигнал на выходе появится с задержкой,

равной длительности тактового импульса.

Очень часто необходимо использовать триггер для деления частоты входной последовательности импульсов на два, т. е. производить переключение триггера в новое состояние каждым входным импульсом (фронтом или спадом). Такой триггер называют счетным, или T-триггером (от англ. Toggle). Он имеет один управляющий вход Т. В сериях выпускаемых микросхем T-триггеров нет. Но триггер такого типа может быть создан на базе синхронного RS-триггера с динамическим управлением, если прямой выход Q соединить с инверсным входом /S, а инверсный выход /Q соединить с инверсным входом /R. На вход синхронизации С подать входную последовательность импульсов (т. е. это будет T-вход). На рис. 2.42 показана схема такого триггера и временные диаграммы его работы.

Рис.

2.42. T-триггер, его обозначение и временные диаграммы.

2.42. T-триггер, его обозначение и временные диаграммы.Аналогичным образом Т-триггер может быть собран на синхронном двухступенчатом RS-триггере.

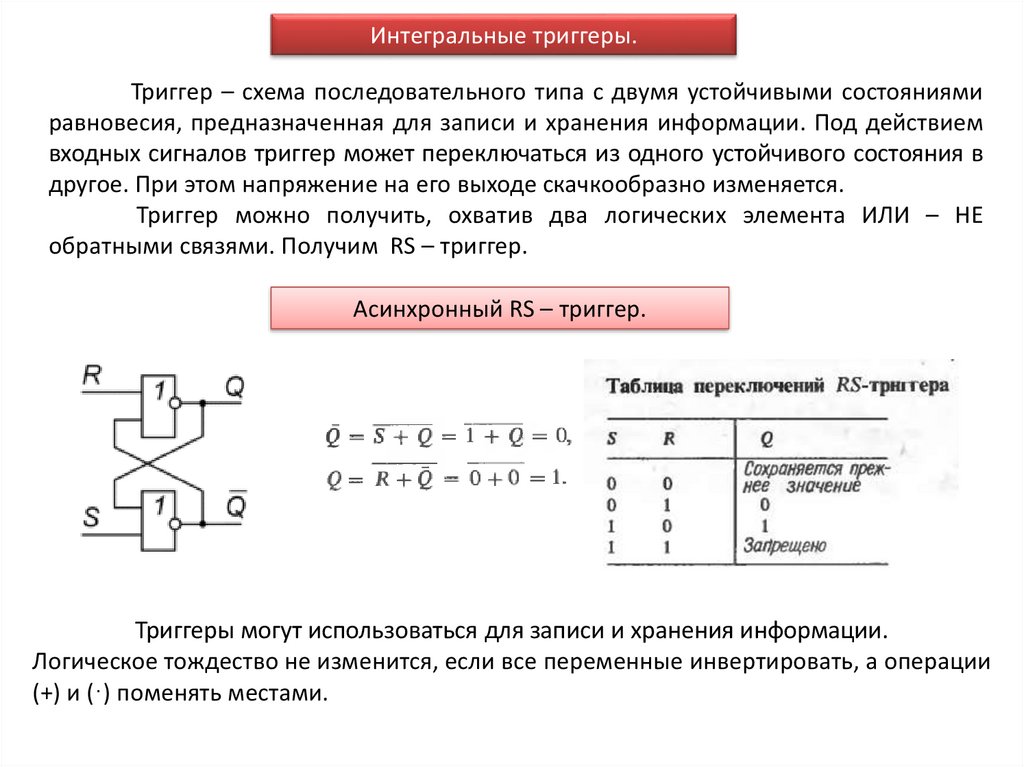

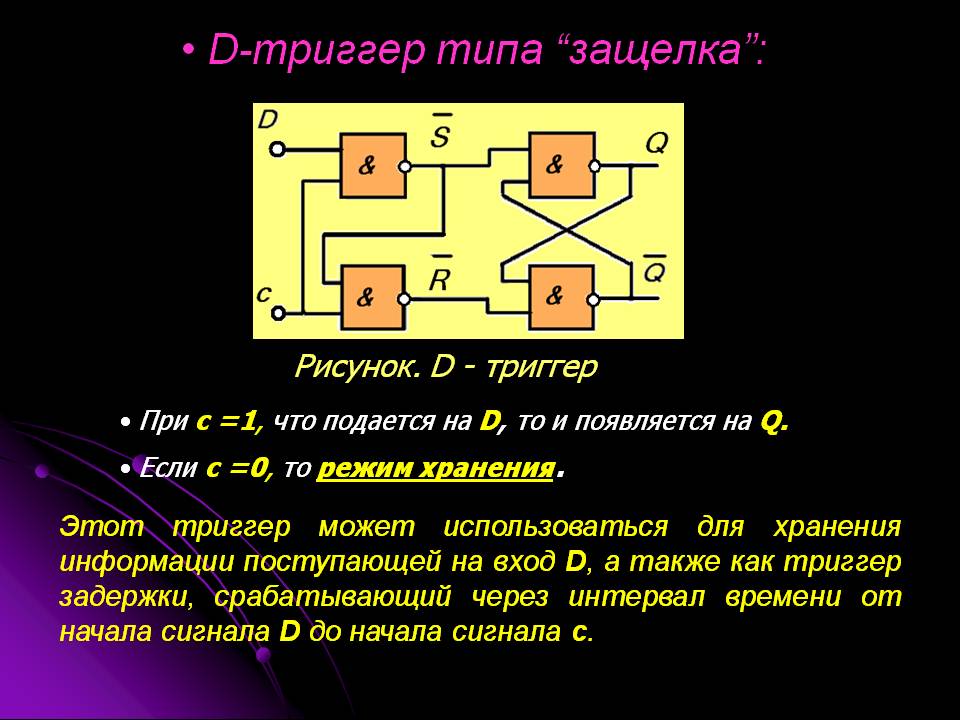

Триггер

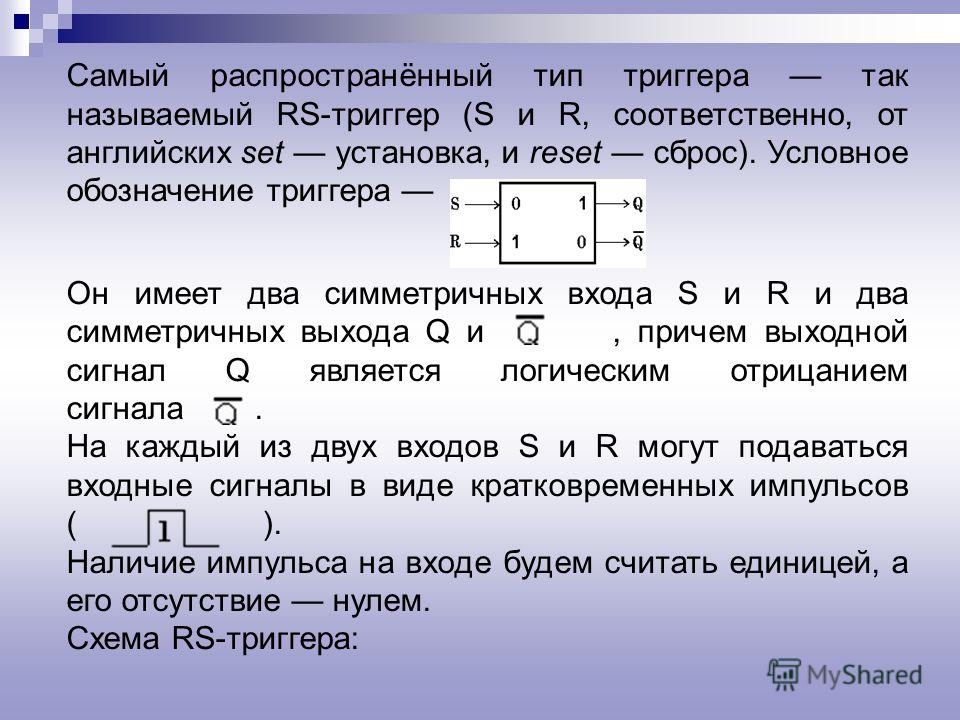

Для реализации хранения данных в оперативной памяти компьютера и внутренних регистрах процессора необходимо устройство способное находится в двух устойчивых состояниях (0 и 1). Такое устройство было изобретено советским ученым-радиотехником Михаилом Александровичем Бонч-Бруевичем в 1918 году на основе лампового триода. В последствие этот элемент получил название триггер (англ.trigger – «спусковой крючок», в общем смысле, приводящий нечто в действие).

Триггер — устройство, способное длительное время находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов.

Один триггер способен хранить один бит данных. Соответственно, для хранения 1 байта информации потребуется 8 триггеров, а для 1 килобайта – 8 • 1024 подобных элемента. Очевидно, что современные объемы оперативной памяти компьютера содержат миллионы триггеров.

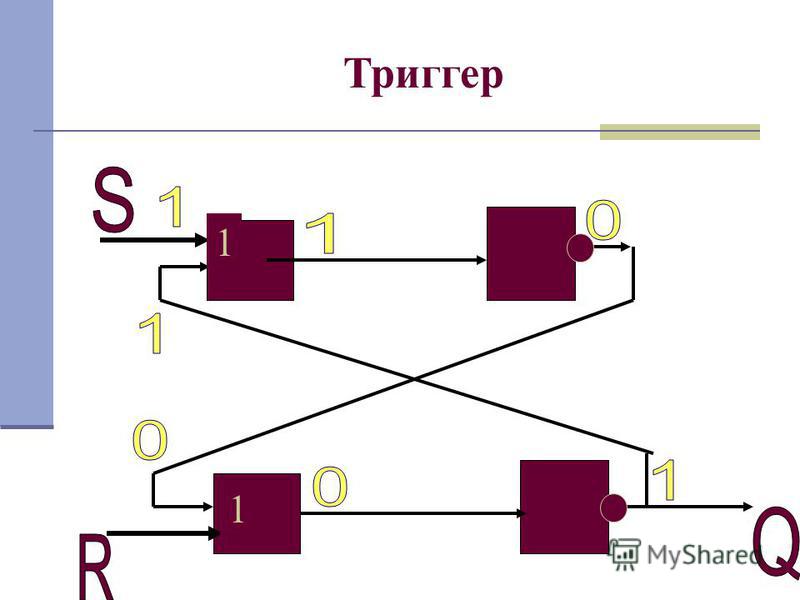

Существует несколько видов триггеров. Одним из самых распространённых является RS-триггер. Rs-триггер можно построить на двух дизъюнкторах и двух инверторах. На рисунке 1 показано условное обозначение триггера (слева) и его устройство на указанных логических элементах.

Триггер имеет два входа S (от англ. set — установить) и R (от англ. reset — сброс), на которые поступают управляющие сигналы и два выхода — Q и ¬ Q. Основным выходом является Q.

Для реализации возможности хранения информации в устройстве триггера используется обратная связь. Под обратной связью понимают подачу выходного сигнала на вход устройства. Обратная связь имеет перекрестный характер (см. рис.1). Дополнительный выход ¬ Q используется только для обратной связи.

Построим таблицу истинности для триггера.

- S = 0, R = 0. В этом случае на вход элемента «ИЛИ» в нижней ветке поступит сигнал ¬ Q + 0 = ¬ Q. Значит, на выходе Q остается прежнее значение. Аналогично, нетрудно заметить, что сигнал ¬ Q также не меняет своего значения.

Таким образом, в данном режиме триггер хранит предыдущее состояние.

Таким образом, в данном режиме триггер хранит предыдущее состояние. - S = 0, R = 1. Т. к. на вход R поступает 1, то на выходе элемента «ИЛИ» в нижней ветке схемы будет 1, а на выходе «НЕ» — ноль. Значит, Q = 0. Тогда на входы элемента «ИЛИ» в верхней ветке поступает два нуля, а на выходе ¬ Q имеем 1. Выход Q является основным, значит, в триггер записан 0.

- S = 1, R = 0. В силу симметрии схемы (см. рис.1), легко заметить, что в этом случае в триггер будет записана 1.

- S = 1, R = 1. Такая комбинация входных сигналов может привести к неоднозначному результату, поэтому такой вариант запрещен.

| S | R | Q | ¬ Q | Режим работы триггера |

|---|---|---|---|---|

| 0 | 0 | Q | ¬ Q | Хранение бита |

| 0 | 1 | 1 | 0 | Сброс в 0 |

| 1 | 0 | 0 | 0 | Установка в 1 |

| 1 | 1 | 1 | 1 | Запрещено |

Запуск триггеров — вопросы и ответы по цифровым схемам

Этот набор вопросов и ответов с множественным выбором по цифровой электронике/схемам (MCQ) посвящен теме «Запуск триггеров».

1. Характеристическое уравнение J-K-триггера ______________

a) Q(n+1)=JQ(n)+K’Q(n)

b) Q(n+1)=J’Q(n )+KQ'(n)

c) Q(n+1)=JQ'(n)+KQ(n)

d) Q(n+1)=JQ'(n)+K’Q(n)

View Answer

Ответ: d

Объяснение: Характеристическое уравнение необходимо, когда для определенного вентиля требуется определенный выход, чтобы удовлетворить таблицу истинности. Характеристическое уравнение JK-триггера имеет вид: Q(n+1)=JQ'(n)+K’Q(n).

2. В J-K-триггере, если J=K, результирующий триггер обозначается как _____________

a) D-триггер

b) S-R-триггер

c) T-триггер

d) S-K триггер

Просмотреть ответ

Ответ: c

Объяснение: В триггере J-K, если оба входа одинаковы, он ведет себя как триггер T.

3. В J-K-триггере функция K=J используется для реализации _____________

a) D-триггер

b) S-R-триггер

c) T-триггер

d) S-K-триггер

Вид Ответ

Ответ: c

Объяснение: Т-триггер допускает те же входы. Итак, в JK-триггере J=K он будет работать как T-триггер.

Итак, в JK-триггере J=K он будет работать как T-триггер.

Примечание: присоединяйтесь к бесплатным классам Sanfoundry в Telegram или Youtube

реклама

реклама

4. Единственная разница между комбинационной схемой и триггером заключается в том, что _____________

а) триггеру требуется предыдущее состояние

б) Триггеру требуется следующее состояние

c) Триггеру требуется тактовый импульс

d) Триггер зависит как от прошлого, так и от настоящего состояния

Просмотреть ответ

Ответ: c

Объяснение: И триггер, и защелки являются элементами памяти с тактовыми/управляющими входами. Они зависят как от прошлого, так и от настоящего состояния. Тогда как в случае комбинационных схем они зависят только от текущего состояния.

5. Сколько устойчивых состояний имеют комбинационные схемы?

a) 3

b) 4

c) 2

d) 5

Посмотреть ответ

Ответ: c

Пояснение: Два устойчивых состояния комбинационных схем — 1 и 0. Тогда как в триггерах есть дополнительное состояние известный как Запретное государство.

Тогда как в триггерах есть дополнительное состояние известный как Запретное государство.

Пройдите пробные тесты цифровых схем — по главам!

Начать тест сейчас: глава 1,

2,

3,

4,

5,

6,

7,

8,

9,

10

6. Триггер активируется только _____________

a) Триггер по положительному фронту

b) Триггер по отрицательному фронту

c) Триггер по положительному или отрицательному фронту

d) Триггер по синусоиде

View Answer

Ответ: c

Объяснение : триггеры можно активировать с помощью триггера положительного или отрицательного фронта.

7. Защелка S-R, состоящая из вентилей НЕ-И, называется цепью с активным низким уровнем, потому что ___________

a) Активируется только триггером положительного уровня

b) Активируется только триггером отрицательного уровня

c) Активируется только триггером положительного или отрицательного уровня

d) Активируется только синусоидальным триггером

View Answer

Ответ: b

Объяснение: Активный низкий уровень означает, что только входное значение 0 устанавливает или сбрасывает схему.

реклама

8. Триггеры J-K и T являются производными от основного ___________

a) Триггер S-R

b) Защелка S-R

c) Защелка D

d) Триггер D

Просмотреть ответ

Ответ: b

Объяснение: Защелка SR является базовым блоком для D-триггера/триггера из которые являются производными триггеров JK и T. Защелка похожа на триггер, только без тактового входа.

9. Триггеры, не имеющие недопустимых состояний: _____________

a) S-R, J-K, D

b) S-R, J-K, T

c) J-K, D, S-R

d) J-K, D, T

Вид Ответ

Ответ: d

Объяснение: В отличие от защелки SR, эти цепи не имеют недопустимых состояний. Защелка или триггер SR находится в недопустимом или запрещенном состоянии, в котором невозможно определить ни один выход.

реклама

10. Что означает треугольник на тактовом входе триггера J-K?

a) Уровень включен

b) Срабатывает фронт

c) Оба уровня активируются, и срабатывает фронт

d) Срабатывает уровень

Просмотреть ответ

Ответ: b

Объяснение: Треугольник на тактовом входе триггера J-K означает срабатывание фронта . В то время как отсутствие символа треугольника означает, что триггер срабатывает по уровню.

В то время как отсутствие символа треугольника означает, что триггер срабатывает по уровню.

11. Что означает кружок на тактовом входе триггера J-K?

a) Уровень активирован

b) Сработал положительный фронт

c) Сработал отрицательный фронт

d) Сработал уровень

Просмотреть ответ

Ответ: c

Объяснение: Кружок на тактовом входе триггера J-K означает срабатывание отрицательного фронта. В то время как отсутствие символа треугольника означает, что триггер срабатывает по уровню.

12. Что означает прямая линия на тактовом входе триггера J-K?

a) Уровень активирован

b) Сработал положительный фронт

c) Сработал отрицательный фронт

d) Сработал уровень

Просмотреть ответ

Ответ: d

Объяснение: Прямая линия на тактовом входе триггера J-K сработал средний уровень. Принимая во внимание, что наличие символа треугольника означает, что триггер срабатывает по фронту.

13. Что означает полукруг на тактовом входе триггера J-K?

a) Уровень активирован

b) Сработал положительный фронт

c) Сработал отрицательный фронт

d) Сработал уровень

Просмотреть ответ

Ответ: d

Объяснение: Полукруг на тактовом входе триггера J-K сработал средний уровень. Принимая во внимание, что наличие символа треугольника означает, что триггер срабатывает по фронту.

Принимая во внимание, что наличие символа треугольника означает, что триггер срабатывает по фронту.

14. Триггер J-K с J = 1 и K = 1 имеет тактовый вход 20 кГц. Выход Q: _____________

a) Постоянно НИЗКИЙ

b) Постоянно ВЫСОКИЙ

c) Прямоугольная волна 20 кГц

d) Прямоугольная волна 10 кГц

Посмотреть ответ

Ответ: d

Объяснение: Поскольку используется один триггер, доступны два состояния. Таким образом, на выходе имеется частота 20/2 = 10 Гц.

15. На триггере S-R, запускаемом положительным фронтом, выходы отражают состояние входа, когда ________

a) Тактовый импульс НИЗКИЙ

b) Тактовый импульс ВЫСОКИЙ

c) Тактовый импульс переходит из НИЗКОГО в ВЫСОКИЙ

d) Тактовый импульс переходит из ВЫСОКОГО в НИЗКИЙ

Просмотреть ответ

Ответ: c

Объяснение: Устройство, запускаемое по фронту, будет следовать условию ввода при наличии перехода. Говорят, что положительный фронт срабатывает, когда происходит переход от LOW к HIGH. Хотя говорят, что отрицательный фронт срабатывает, когда происходит переход от ВЫСОКОГО к НИЗКОМУ.

Хотя говорят, что отрицательный фронт срабатывает, когда происходит переход от ВЫСОКОГО к НИЗКОМУ.

Sanfoundry Global Education & Learning Series – Digital Circuits.

Чтобы попрактиковаться во всех областях цифровых схем, вот полный набор из более чем 1000 вопросов и ответов с несколькими вариантами ответов .

Следующие шаги:

- Получите бесплатный сертификат о заслугах в области цифровых схем

- Принять участие в конкурсе сертификации цифровых схем

- Станьте лидером в области цифровых схем

- Пройти тесты цифровых схем

- Практические тесты по главам: глава 1, 2, 3, 4, 5, 6, 7, 8, 9, 10

- Пробные тесты по главам: глава 1, 2, 3, 4, 5, 6, 7, 8, 9, 10

реклама

реклама

Подпишитесь на наши информационные бюллетени (тематические). Участвуйте в конкурсе сертификации Sanfoundry, чтобы получить бесплатный Сертификат отличия. Присоединяйтесь к нашим социальным сетям ниже и будьте в курсе последних конкурсов, видео, стажировок и вакансий!

Участвуйте в конкурсе сертификации Sanfoundry, чтобы получить бесплатный Сертификат отличия. Присоединяйтесь к нашим социальным сетям ниже и будьте в курсе последних конкурсов, видео, стажировок и вакансий!

Ютуб | Телеграмма | Линкедин | Инстаграм | Фейсбук | Твиттер | Пинтерест

Маниш Бходжасиа, ветеран технологий с более чем 20-летним стажем работы в Cisco и Wipro, является основателем и техническим директором компании Sanfoundry . Он живет в Бангалоре и занимается разработкой Linux Kernel, SAN Technologies, Advanced C, Data Structures & Alogrithms. Оставайтесь на связи с ним в LinkedIn.

Подпишитесь на его бесплатные мастер-классы на Youtube и технические обсуждения в Telegram SanfoundryClasses.

Бистабильный мультивибратор — Работа, типы, срабатывание

Бистабильный мультивибратор имеет два абсолютно стабильных состояния. Он будет оставаться в том состоянии, в котором он находится, пока триггерный импульс не заставит его переключиться в другое состояние. Например, предположим, что в любой конкретный момент транзистор Q 1 находится в проводящем состоянии, а транзистор Q 2 находится в состоянии отсечки. Если его предоставить самому себе, бистабильный мультивибратор останется в этом положении навсегда. Однако если на цепь подать внешний импульс так, что Q 1 отключен, а Q 2 включен, цепь останется в новом положении. Затем требуется еще один триггерный импульс, чтобы вернуть схему в исходное состояние.

Например, предположим, что в любой конкретный момент транзистор Q 1 находится в проводящем состоянии, а транзистор Q 2 находится в состоянии отсечки. Если его предоставить самому себе, бистабильный мультивибратор останется в этом положении навсегда. Однако если на цепь подать внешний импульс так, что Q 1 отключен, а Q 2 включен, цепь останется в новом положении. Затем требуется еще один триггерный импульс, чтобы вернуть схему в исходное состояние.

Другими словами, мультивибратор, у которого оба состояния стабильны, называется бистабильным мультивибратором. Его также называют триггером, триггерной схемой или двоичной схемой. Выходной импульс получается, когда и почему на вход подается управляющий (запускающий) импульс. Полный цикл выходного сигнала создается для каждых двух запускающих импульсов правильной полярности и амплитуды.

На рисунке (а) показана схема бистабильного мультивибратора с использованием двух транзисторов NPN. Здесь выход транзистора Q 2 соединен с транзистором Q 1 через резистор R 2 . Аналогично, выход транзистора Q 1 соединен с базой транзистора Q 2 через резистор R 1 . Конденсаторы C 2 и C 1 известны как ускоряющие конденсаторы. Их функция состоит в том, чтобы увеличить скорость схемы при резком переходе из одного устойчивого состояния в другое устойчивое состояние. Базовые резисторы (R 3 и R 4 ) обоих транзисторов подключены к общему истоку (-V BB ). Выход бистабильного мультивибратора имеется на выводе коллектора обоих транзисторов Q 1 и Q 2 . Однако эти два выхода дополняют друг друга.

Здесь выход транзистора Q 2 соединен с транзистором Q 1 через резистор R 2 . Аналогично, выход транзистора Q 1 соединен с базой транзистора Q 2 через резистор R 1 . Конденсаторы C 2 и C 1 известны как ускоряющие конденсаторы. Их функция состоит в том, чтобы увеличить скорость схемы при резком переходе из одного устойчивого состояния в другое устойчивое состояние. Базовые резисторы (R 3 и R 4 ) обоих транзисторов подключены к общему истоку (-V BB ). Выход бистабильного мультивибратора имеется на выводе коллектора обоих транзисторов Q 1 и Q 2 . Однако эти два выхода дополняют друг друга.

Допустим, если Q 1 является проводящим, то тот факт, что точка A находится почти в положении ON, делает основание Q 2 отрицательным (делителем потенциала R 2 — R 4 ) и удерживает Q 2 выкл.

Аналогично при выключенном Q 2 делитель потенциала от V CC до -V BB (R L2 , R 1 , R 1 , R 3 предназначен для удержания базы) Q 1 при напряжении около 0,7 В, что обеспечивает проводимость Q 1 . Видно, что Q 1 удерживает Q 2 ВЫКЛ, а Q 2 удерживает Q 1 ВКЛ.

Предположим, теперь к R приложен положительный импульс. Это вызовет Q 2 провести. Когда коллектор Q 2 падает до нуля, он отключает Q 1 и, следовательно, BMV переключается в другое состояние.

Аналогичным образом, положительный триггерный импульс, поданный на S, вернет BMV в исходное состояние.

Использование:

- В схемах синхронизации в качестве делителя частоты

- В схемах счета

- В схемах памяти компьютера

перевести оба транзистора в активную область, и результирующая регенеративная обратная связь приведет к изменению состояния.

Запуск может быть двух следующих типов:

- Асимметричный запуск

- Симметричный запуск

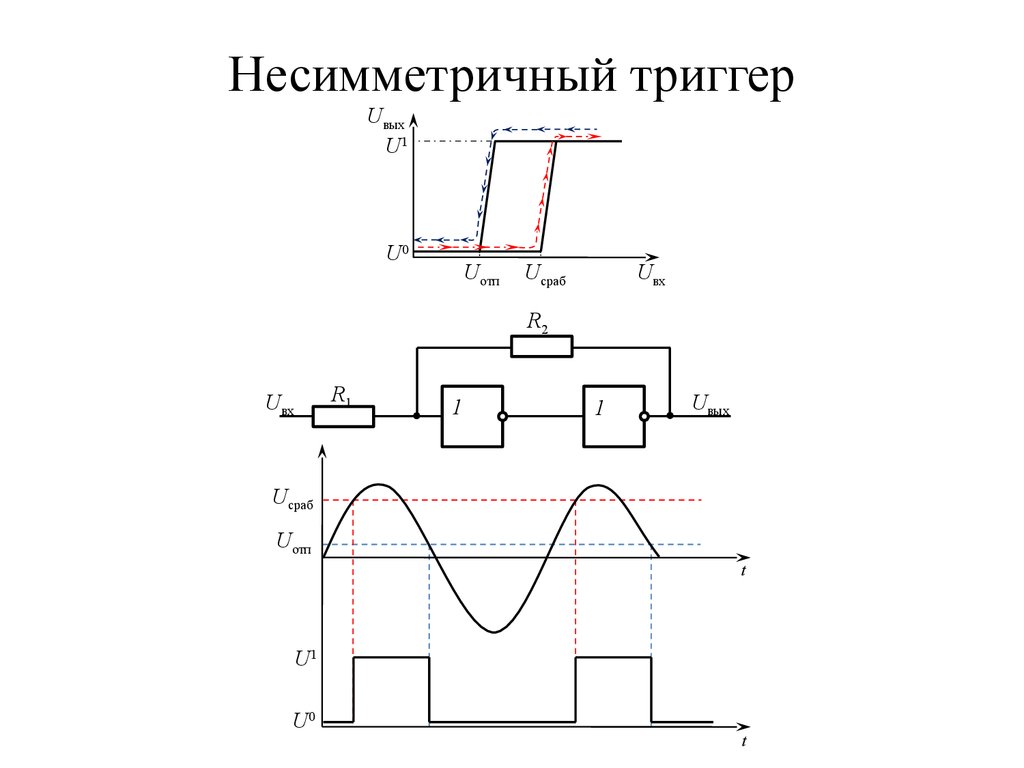

(I) Асимметричный запуск

При асимметричном запуске имеется два входа запуска для транзисторов Q 12 Q1 1 . Каждый вход триггера поступает из отдельного источника триггера. Чтобы вызвать переход между устойчивыми состояниями, скажем, что изначально триггер применяется к бистабильному состоянию. Для следующего перехода теперь такой же триггер должен появиться на транзисторе Q9.0210 2 . Таким образом можно сказать, что при асимметричном запуске триггерные импульсы, полученные от двух отдельных источников и подключенные к двум транзисторам Q 1 и Q 2 по отдельности, последовательно изменяют бистабильное состояние.

На рисунке (b) показана принципиальная схема бистабильного мультивибратора с асимметричным запуском.

Бистабильный нестабильный мультивибратор Первоначально Q 1 выключен, а транзистор Q 2 включен. Первый импульс, полученный от источника триггера A, приложенный к терминалу, выключает его, переводя его из области насыщения в активный транзистор Q 1 включен, а транзистор Q 2 выключен. Любой дальнейший импульс в следующий раз, когда триггерный импульс подается на клемму B, изменение стабильного состояния приведет к включению транзистора Q 2 и выключению транзистора Q 1 .

Первый импульс, полученный от источника триггера A, приложенный к терминалу, выключает его, переводя его из области насыщения в активный транзистор Q 1 включен, а транзистор Q 2 выключен. Любой дальнейший импульс в следующий раз, когда триггерный импульс подается на клемму B, изменение стабильного состояния приведет к включению транзистора Q 2 и выключению транзистора Q 1 .

Асимметричный запуск находит применение при генерации стробирующего сигнала, длительность которого определяется любыми двумя независимыми событиями, происходящими в разные моменты времени. Таким образом, измерение временного интервала облегчается.

(II) Симметричный запуск

Существуют различные методы симметричного запуска, называемые симметричным коллекторным запуском, симметричным базовым запуском и симметричным гибридным запуском. Здесь мы хотели бы объяснить только симметричное срабатывание по базе (положительный импульс) только в том виде, в каком оно дано в разделе «Симметричное срабатывание по базе».

На рисунке (c) показана принципиальная схема двоичной схемы с симметричным запуском по базе с применением положительных импульсов запуска.

Бистабильный нестабильный мультивибраторДиоды Д 1 и Д 2 — управляющие диоды. Здесь положительные импульсы, попробуйте включить и выключить транзистор. Таким образом, когда транзистор Q 1 выключен, а транзистор Q 2 включен, соответствующие базовые напряжения и V B1N , OFF и V B2N , ON . Видно, что V B1N , OFF > V B1N , ON . Таким образом, диод D 2 имеет большее обратное смещение по сравнению с диодом D 1 .

При появлении положительного дифференцированного импульса амплитудой более (V B1N , OFF + Vɣ) диод D 1 смещается в прямом направлении, а транзистор Q 1 входит в активную область и с последующая регенеративная обратная связь Q 1 включается, а транзистор Q 2 выключается.

22.

22. Таким образом, в данном режиме триггер хранит предыдущее состояние.

Таким образом, в данном режиме триггер хранит предыдущее состояние.